# Implementación del procesador Cortex<sup>TM</sup>-M0 DesignStart en una FPGA de rango bajo

Pedro Ignacio Martos y Fabricio Baglivo

Laboratorio de Sistemas Embebidos, Facultad de Ingeniería – UBA, Buenos Aires, Argentina.

# ARM Cortex<sup>TM</sup>-M

- Procesadores de 32 bits

- Bajo costo (~ U\$S3 LPC1100)

- Bajo consumo

- Set de instrucciones de alta densidad

- o Fácil de usar

- Alta performance

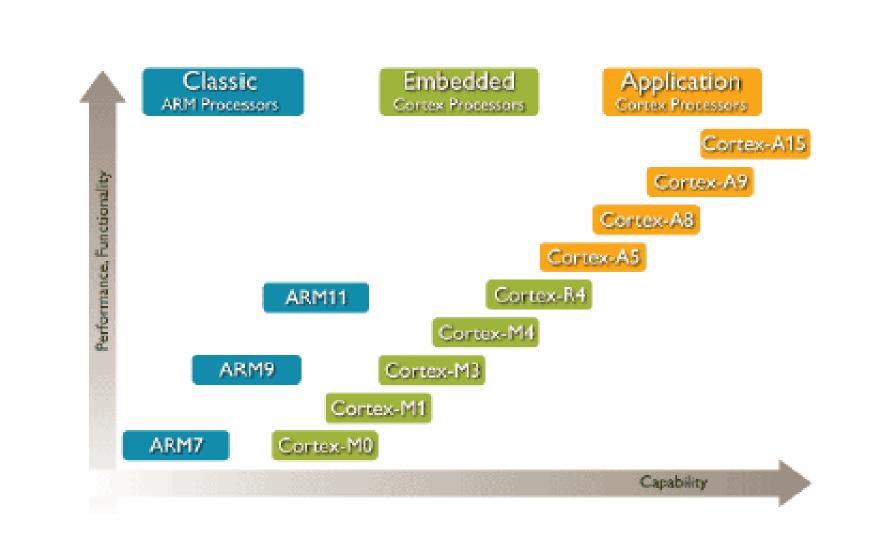

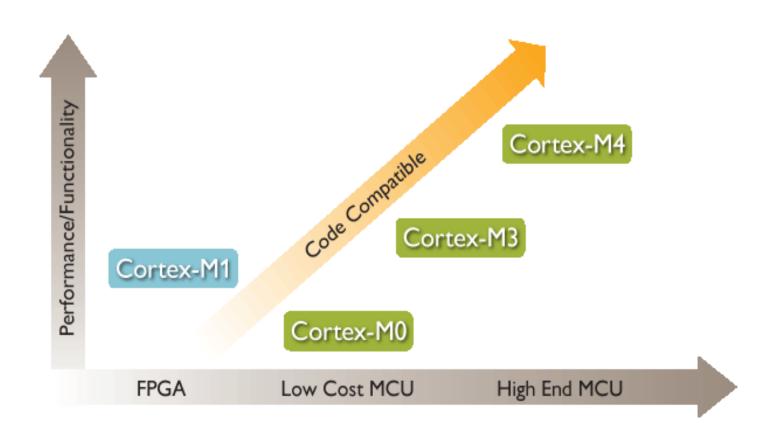

### Cortex<sup>TM</sup> M vs otros Cortex

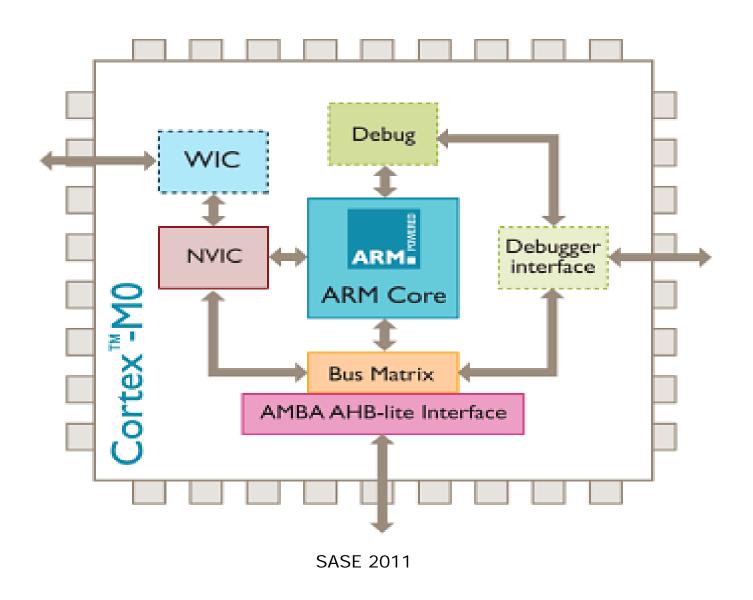

# Cortex<sup>TM</sup>-M0

- Es el más pequeño de la familia Cortex<sup>™</sup>-M

- consume 85 microwatts/MHz

- Frec. = 40 50 MHz

### Cortex-M0

5

#### Protocolo AMBA

- AMBA → estandar de interconexión de bloques funcionales

- o Características:

- Flexible

- Multi capas -> permite trabajar con varios Maestros y Esclavos

- Compatibilidad

- Soporte de 3ros

### AMBA versión 3

- AXI → interfaz de comunicación con 5 canales de alta velocidad.

- O AHB → interfaz de comunicación de 1 solo canal para conexión con periféricos simples.

- O APB → interfaz que soporta conexiones con periféricos de bajo ancho de banda, utilizado para configurar registros e intercambio de datos. Es una inerfaz de bajo consumo.

- ATB → interfaz utilizada para debugging

### AMBA 3 ABH-Lite

- Es una simplificación de ABH

- o Implementa:

- o Comunicaciones de tipo "rafaga"

- Operaciones por flanco de clock

- o sin tri-state

- Configuración de ancho de bus en: 64,

128, 512 y 1024 bits

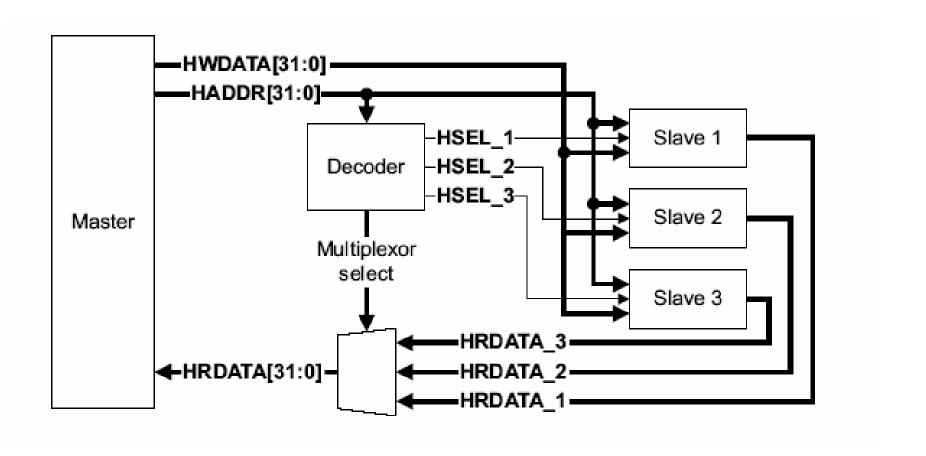

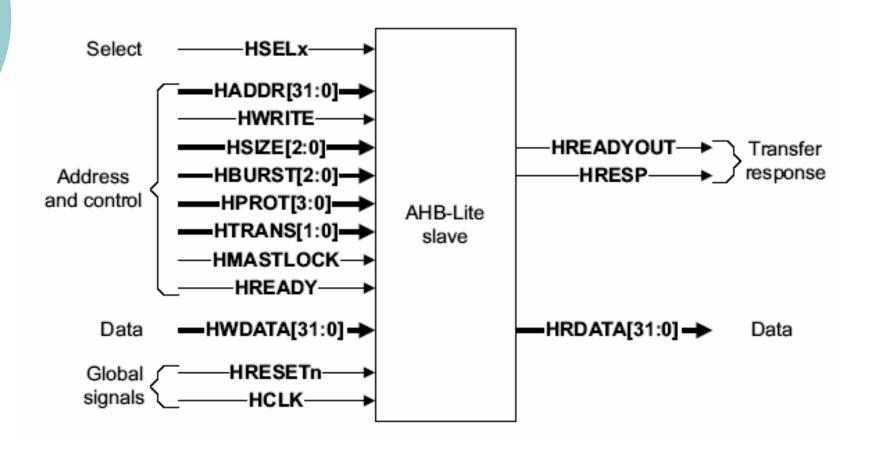

### Esquema de conexión: AHB-Lite

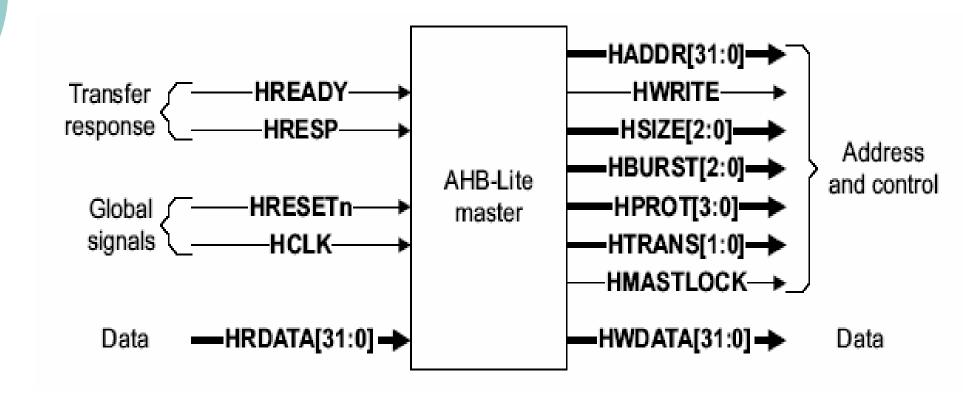

### Maestro en AHB-Lite

### Esclavo en AHB-Lite

# Señales importantes en AHB-Lite

| Globales | Maestro a Esclavo | Esclavo a Maestro |

|----------|-------------------|-------------------|

| HCLK     | HADDR[31:0]       | HRDATA[31:0]      |

| HReset   | HBURST[2:0]       | HREADY            |

|          | HMASTLOCK         | HRESP             |

|          | HPROT[3:0]        |                   |

|          | HSIZE[2:0]        |                   |

|          | HTRANS[1:0]       |                   |

|          | HWDATA[31:0]      |                   |

|          | HWRITE            |                   |

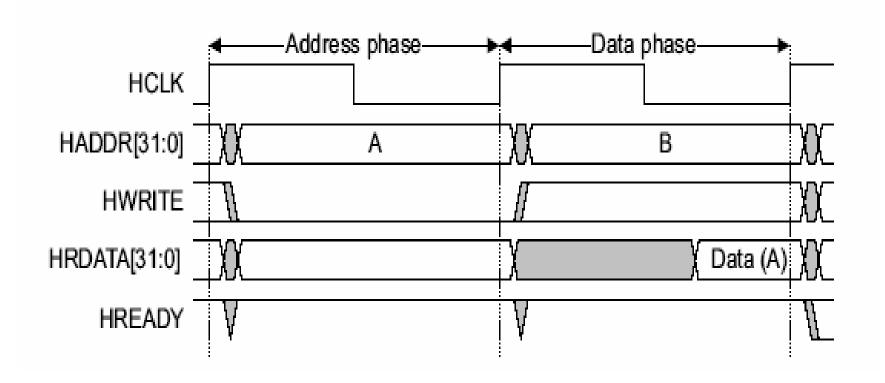

# Ciclo básico de Lectura

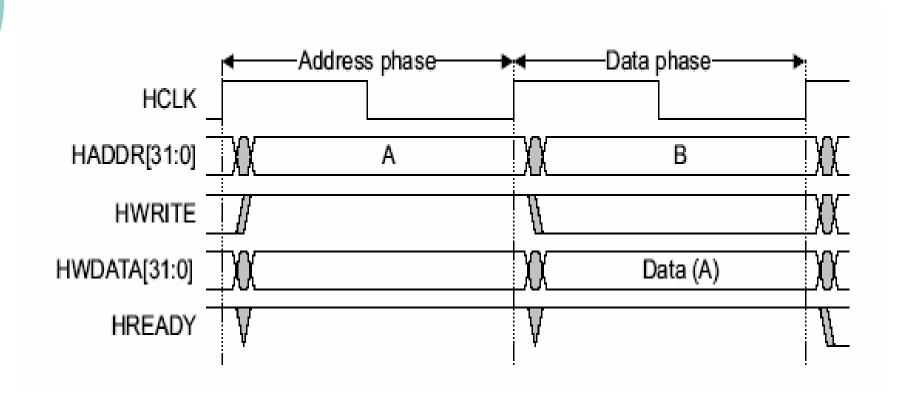

# Ciclo básico de Escritura

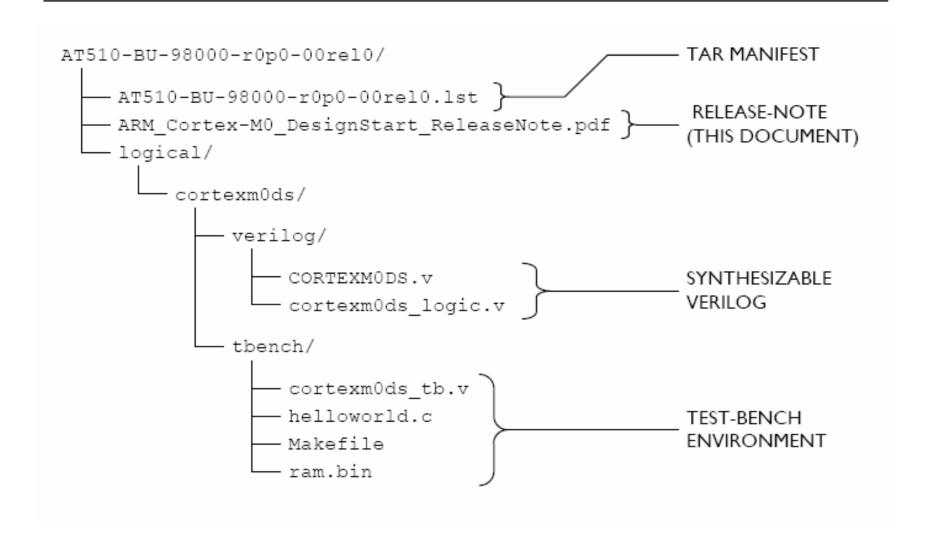

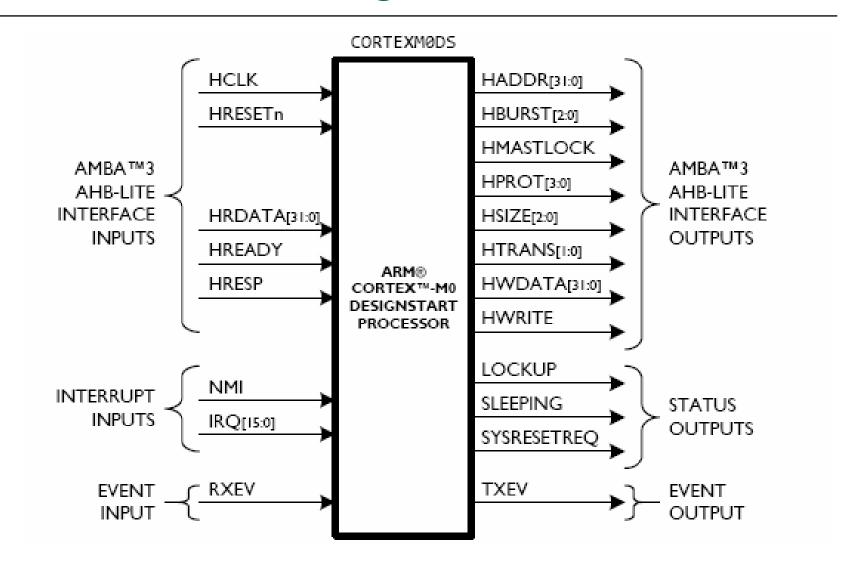

# Cortex M0 DesignStart

Es una configuración fija del Cortex-M0:

- Implementable tanto en software como en hardware

- Se distribuye en lenguaje Verilog totalmente sintetizable

# Cortex M0 DesignStart

# Cortex M0 DesignStart

# Cortex-M – Características

| RISC processor core                                                                                                                      | Thumb-2 <sup>®</sup> technology                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| High performance 32-bit CPU     Deterministic operation     Low latency 3-stage pipeline                                                 | <ul> <li>Optimal blend of 16/32-bit instructions</li> <li>3x smaller code size than 8-bit devices</li> <li>No compromise on performance</li> </ul> |

| Low power modes                                                                                                                          | Nested Vectored Interrupt Controller<br>(NVIC)                                                                                                     |

| Integrated sleep state support     Multiple power domains     Architected software control                                               | Low latency, low jitter interrupt response     No need for assembly programming     Interrupt service routines in pure C                           |

| Tools and RTOS support                                                                                                                   | CoreSight debug and trace                                                                                                                          |

| Broad 3rd party tools support     Cortex Microcontroller     Software Interface Standard     (CMSIS)     Maximizes software effort reuse | JTAG or 2-pln Serial Wire Debug<br>(SWD) connection     Support for multiple processors     Support for real-time trace                            |

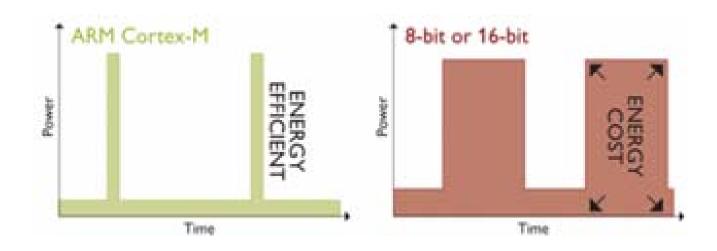

### Cortex-M - Características

- Tienen mejor manejo de los modos de bajo consumo.

- Trabajan a baja frecuencia y con ciclos de actividad más cortos

### Cortex-M – Características

- Fabricado por diferentes empresas

- Atmel, Actel, NXP, Cypress, Samsung, Texas Instruments, ST, etc

- Compatibilidad de código entre ellos

- Herramientas unificadas y para diversos OS

SASE 2011 2 O VOIVE

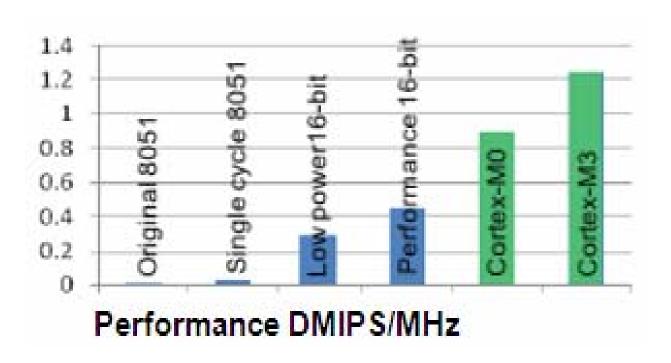

# Cortex-M – Comparacion de performance

# Cortex-M – capacidades relativas de la familia

# Cortex-M0 – Características

#### » ARM Cortex-M0 Features

| Cortex-M0             |                                                                                                                  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------|--|

| Architecture          | ARMv6-M (Von Neumann)                                                                                            |  |

| ISA support           | Thumb®/ Thumb-2 technology*                                                                                      |  |

| Pipeline              | 3-stage                                                                                                          |  |

| Dhrystone             | 0.9 DMIPS/MHz                                                                                                    |  |

| Interrupts            | NMI + 1 to 32 physical interrupts                                                                                |  |

| Interrupt latency     | 16 cycles                                                                                                        |  |

| Sleep modes           | Integrated WFI and WFE instructions Sleep & Deep Sleep Signals Optional Retention Mode with Power Management Kit |  |

| Enhanced Instructions | Single-cycle (32x32) multiply                                                                                    |  |

| Debug                 | JTAG or Serial-Wire Debug ports                                                                                  |  |

# Cortex-M0 – Mapa de memoria

|                            | 0×FFFFFFF                            |

|----------------------------|--------------------------------------|

| Device 511MB               |                                      |

| Private peripheral bus 1MB | 0×E000000<br>0×E0000000              |

| External device 1.0GB      | 0×DFFFFFFF                           |

| External RAM 1.0GB         | 0×9FFFFFFF                           |

| Peripheral 0.5GB           | 0×5FFFFFF                            |

| SRAM 0.5GB                 | 0×4000000<br>0×3FFFFFF<br>0×20000000 |

| Code 0.5GB                 | 0×1FFFFFF                            |

|                            | 0×00000000                           |

# Implementación en FPGA

### Etapas

- Desarrollo del software

- o Implementación del sistema

- Simulación Funcional

- Verificación en Hardware

- Entorno de desarrollo: Keil ARM MDK

- Proyecto básico: se accede a constantes predefinidas a intervalos regulares.

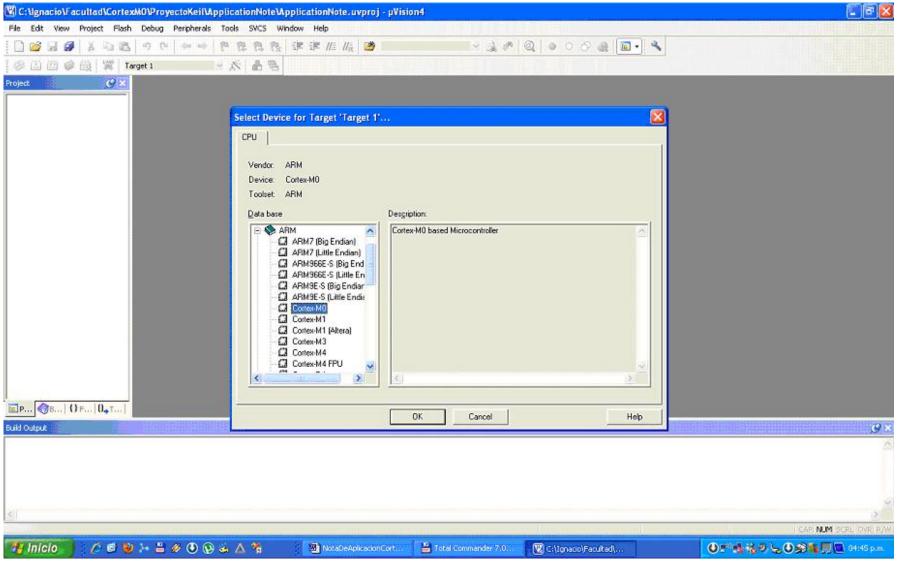

Se crea un proyecto nuevo seleccionando el procesador ARM Cortex-MO

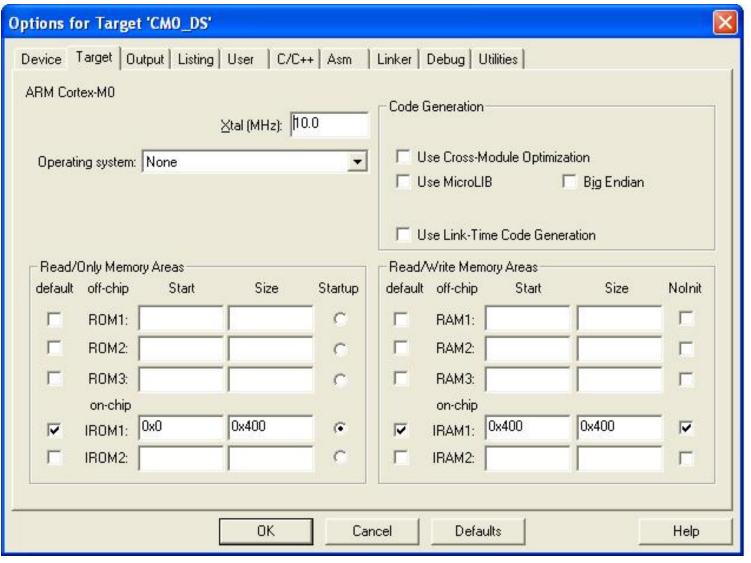

Se deben configurar las áreas de memoria ROM y RAM en forma contigua a fin de que la implementación se realice con una memoria RAM predefinida

- Hay dos archivos de código fuente:

- Main.c con el programa

- Vectors.c con los vectores de interrupción

```

#define LedOn

0xaaaa5555

#define LedOff

0xf0f0f0f0

int main(void)

unsigned int counter;

// dummy

unsigned int ii;

// loop iterator

unsigned int trap; // memory access pattern receiver

unsigned int period; // time interval for memory access

//period=20000000; // roughly 3 seconds for a 10MHz osc in CM0_DS

period=200; // period for simulations

while (1)

counter=0;

for (ii=0;ii<period;ii++)

counter++;

// memory access pattern (turn on)

trap=LedOn;

for (ii=0;ii<period;ii++)

counter++:

trap=LedOff; // memory access pattern (turn off)

// dummy

trap++;

SASE 2011

```

32

```

// Vectors.c

// Define where the top of memory is.

#define TOP_OF_RAM 0x400U

extern int main(void); // Use C-library initialization function.

__attribute__ ((section("__Vectors")))

static void (* const vector_table[])(void) =

(void (*)(void)) TOP_OF_RAM, // Initial value for stack pointer.

(void (*)(void)) main, // Reset handler is C initialization.

// No HardFault handler, just cause lockup.

0,

// No NMI handler, just cause lockup.

0,

// Additional handlers would be listed here.

0//...

};

```

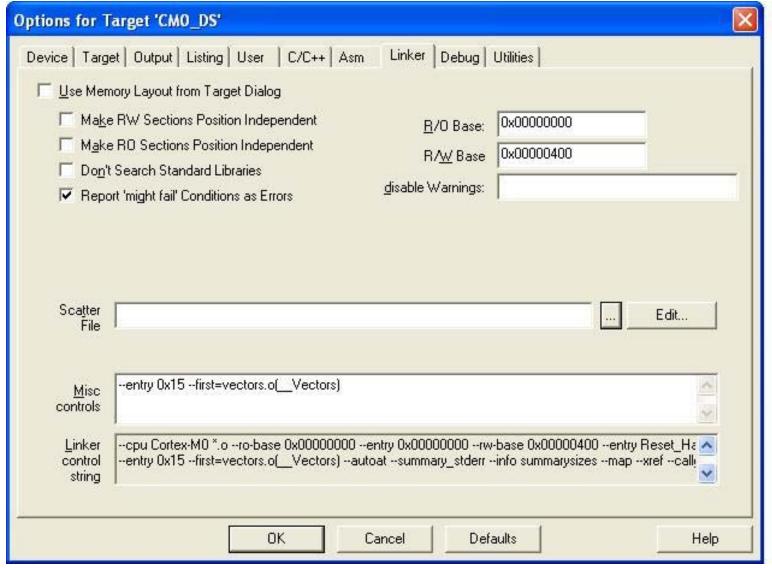

Para que el linker tome la información del archivo vectors.c es necesario agregar la opción "--entry 0x15 --first=vectors.o(\_\_vectors)"

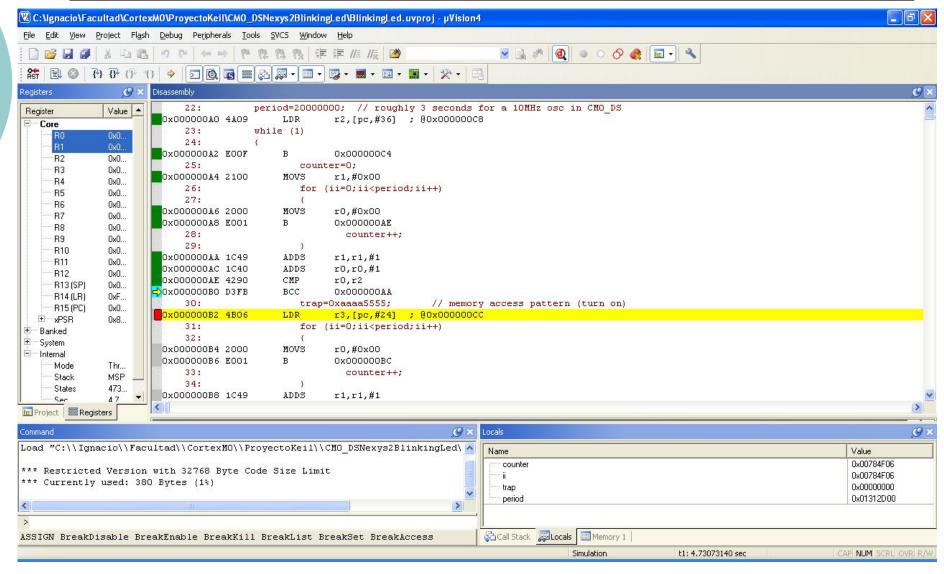

Se realiza el compilado y simulación del código fuente, viéndose en el assembler generado el acceso a las constantes predefinidas (0xaaaa5555 y 0xf0f0f0f0)

### Desarrollo de software

### Logros de esta etapa

- Un proyecto de software en el entorno de desarrollo ARM MDK correctamente configurado para el procesador Cortex-MO DesignStart.

- Un código "main.c" y un código "vectors.c" preparados para ejecutar un programa y con los vectores de interrupción y stack configurados.

- Una simulación exitosa del código fuente.

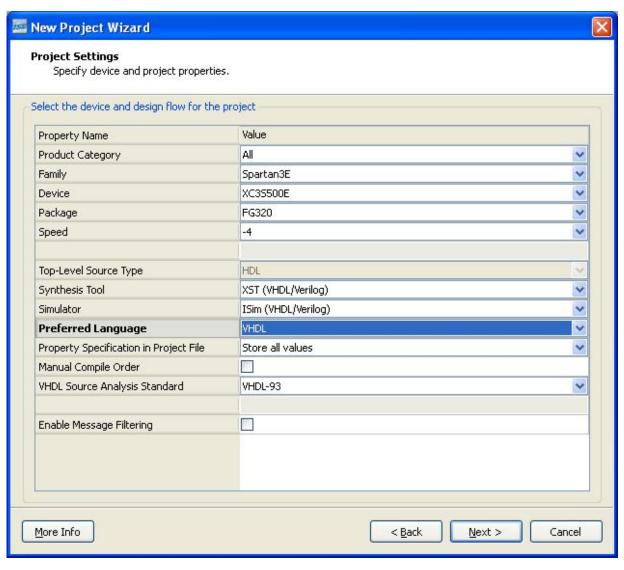

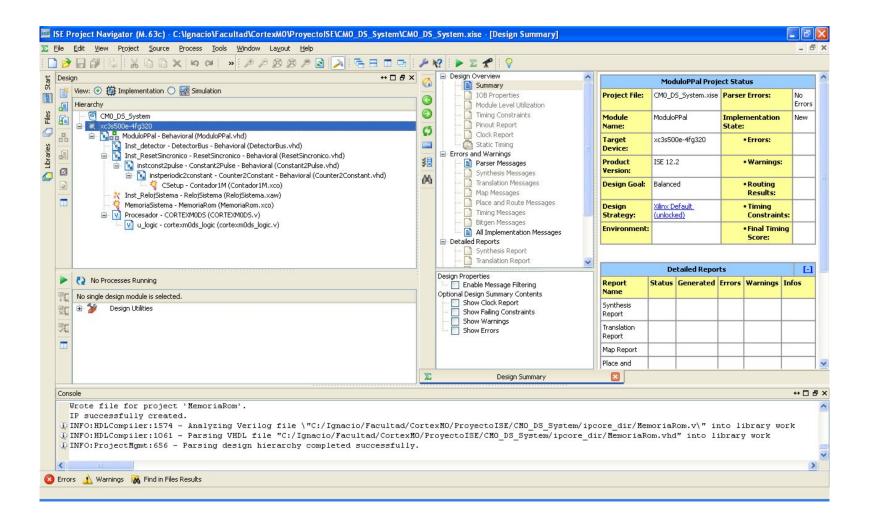

#### Características:

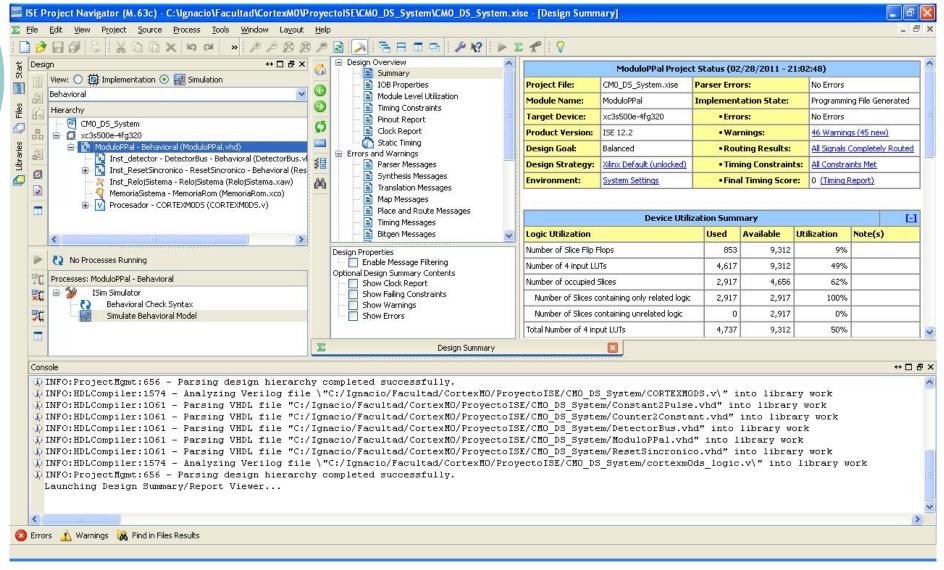

- Implementación de un sistema mínimo en el entorno Xilinx ISE

- Descripción de hardware mixta (VHDL y Verilog)

- Un detector de patrones en el bus de datos comanda un led.

- Utilización de una FPGA Spartan3E-500 en una placa de desarrollo de bajo costo (Nexys2)

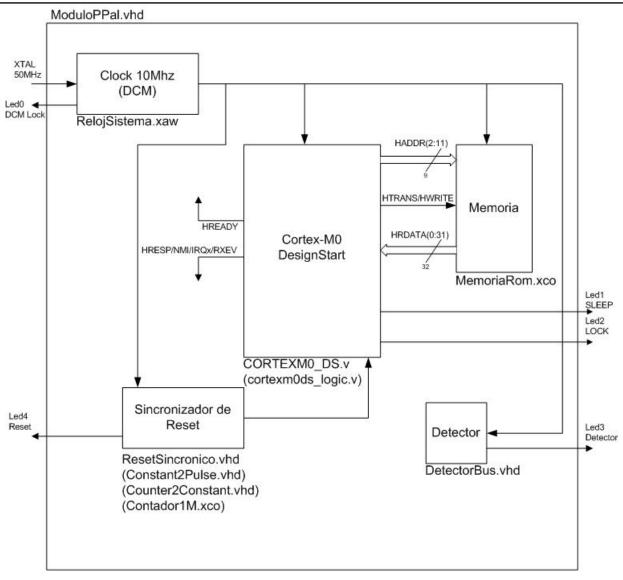

### Bloques del sistema:

- Procesador

- o Memoria

- Reloj

- Reset Sincrónico

- Detector

#### Procesador

- Se utilizan las descripciones en verilog provistas en los deliverables:

- "cortexm0ds\_logic.v" (implementación)

- "CORTEXMODS.v" (interfase y buses)

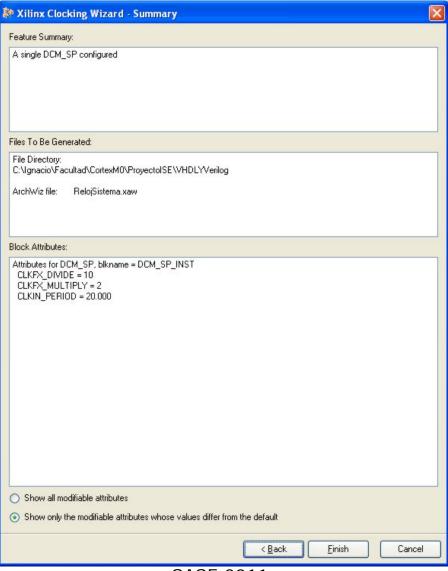

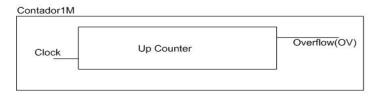

### Reloj

- Se utiliza un DCM (primitiva de Xilinx) cuya entrada es el oscilador de 50 MHz de la placa Nexys2

- Se lo configura para 10 MHz (se pueden utilizar velocidades de hasta alrededor de 40 MHz)

#### Detector

- Esta conectado al bus HRDATA del procesador (datos de lectura)

- o Configurado para detectar patrones:

- Oxaaaa5555 Enciende el led

- Oxf0f0f0f0 Apaga el led

#### Reset sincrónico

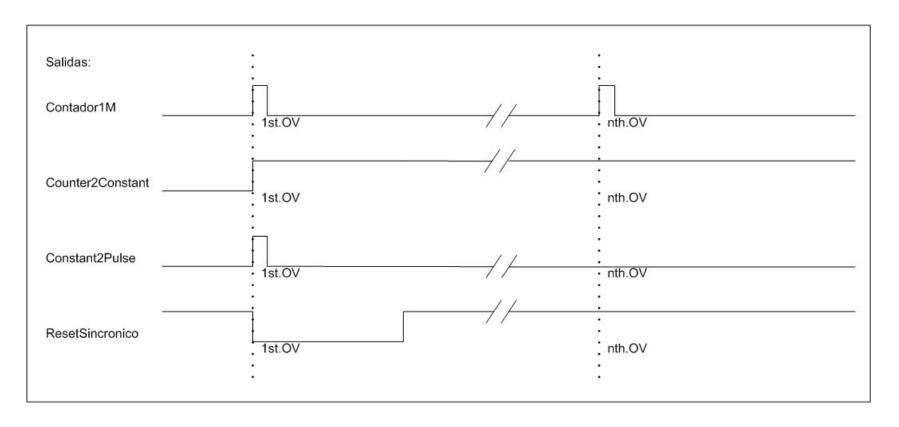

- Se debe generar un único pulso de al menos 2 ciclos de reloj sincronizado con el reloj de sistema

- Se utiliza un contador como base, pero tiene el inconveniente de generar pulsos de un ciclo de reloj de duración y periódicos con el overflow del contador (reset periódico)

### Reset sincrónico (cont.)

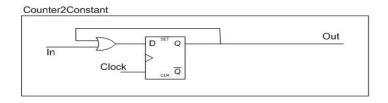

- Se implementan módulos en cascada con la salida periódica del contador

- Counter2Constant: genera una transición de 0 a 1 en el primer rebalsamiento del contador, manteniendo su salida constante aunque en su entrada se reciban los subsiguientes pulsos de rebalsamiento del contador

### Reset sincrónico (cont.)

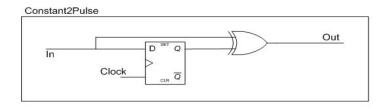

Constant2Pulse: genera un pulso de un ciclo de reloj de duración sincronizado con la transición de 0 a 1 de la salida del módulo Counter2Constant

### Reset sincrónico (cont.)

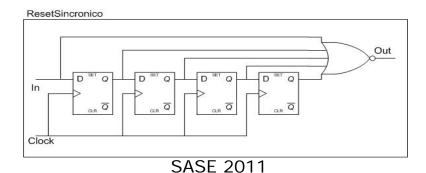

ResetSincronico: recibe como entrada la salida del módulo Constat2Pulse, la invierte, y genera un pulso negativo de 5 ciclos de reloj de duración, que se utiliza como señal de reset del procesador

#### Diagrama de Tiempos

### Diagramas circuitales

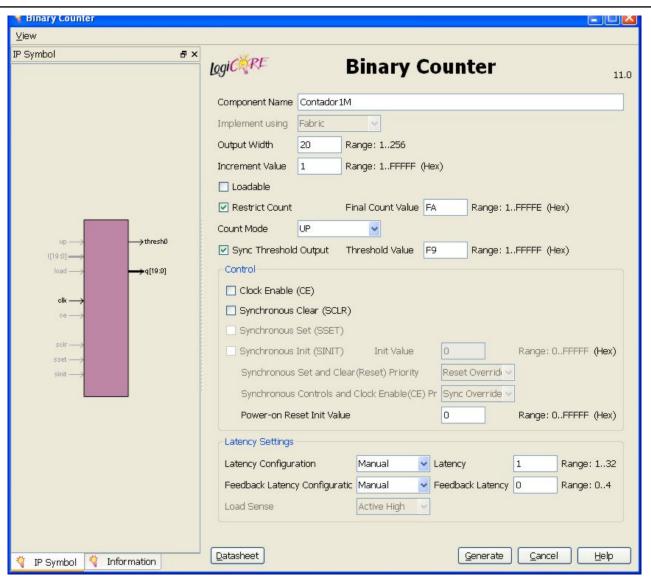

Configuración del contador

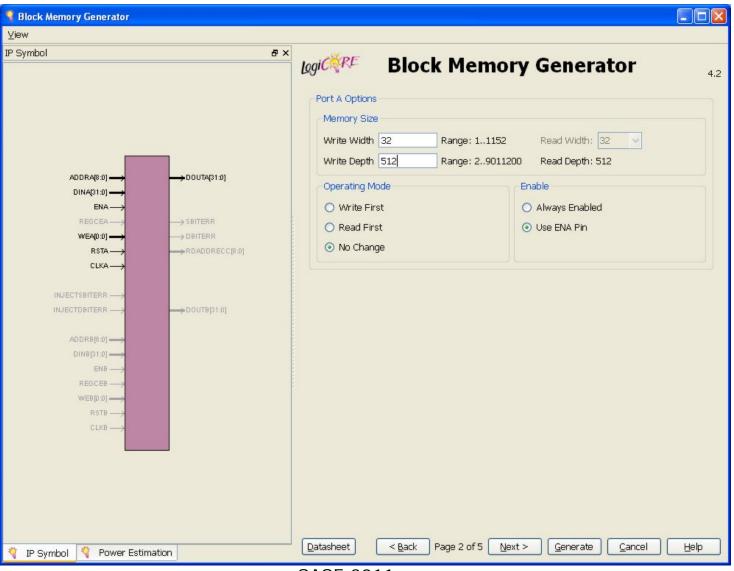

#### Memoria

- Capacidad 512 palabras de 32 bits (2048 bytes)

- 0-255 para la ROM

- 256-511 para la RAM

- Realizada a partir de BlockRAM (primitiva de Xilinx)

- Preinicializada con el programa generado en el entorno ARM MDK

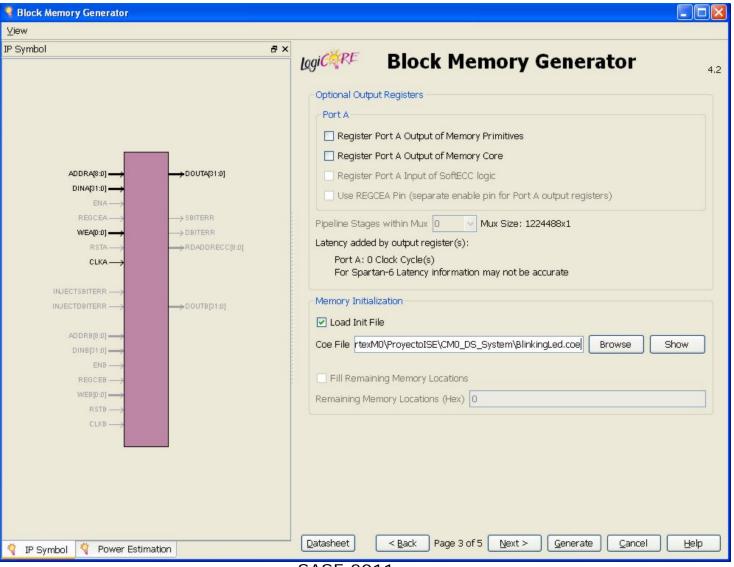

#### Preinicialización:

- Se debe pasar de formato .ELF a una imagen binaria

- Se utiliza la herramienta de línea de comandos "fromelf" provista en ARM MDK

- "fromelf --bin -o BlinkingLed.bin BlinkingLed.axf"

#### Preinicialización:

- Del formato binario se debe pasar al formato de inicialización de Xilinx (.COE)

- Para ello se utiliza la herramienta de línea de comandos "bin2coe", desarrollada especificamente para esta aplicación

"bin2coe BlinkingLed.bin BlinkingLed.coe 512"

#### Preinicialización:

Se utiliza el archivo BlinkingLed.coe generado como archivo de inicialización de contenidos de la memoria

### Logros de esta etapa

- Un proyecto en el entorno Xilinx ISE con un sistema basado en el procesador Cortex-MO

- Sistema configurado y con los bloques mínimos con capacidad para ejecutar un programa prediseñado.

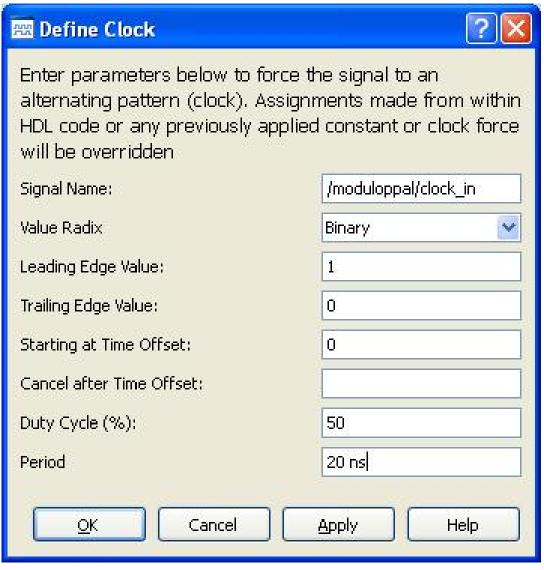

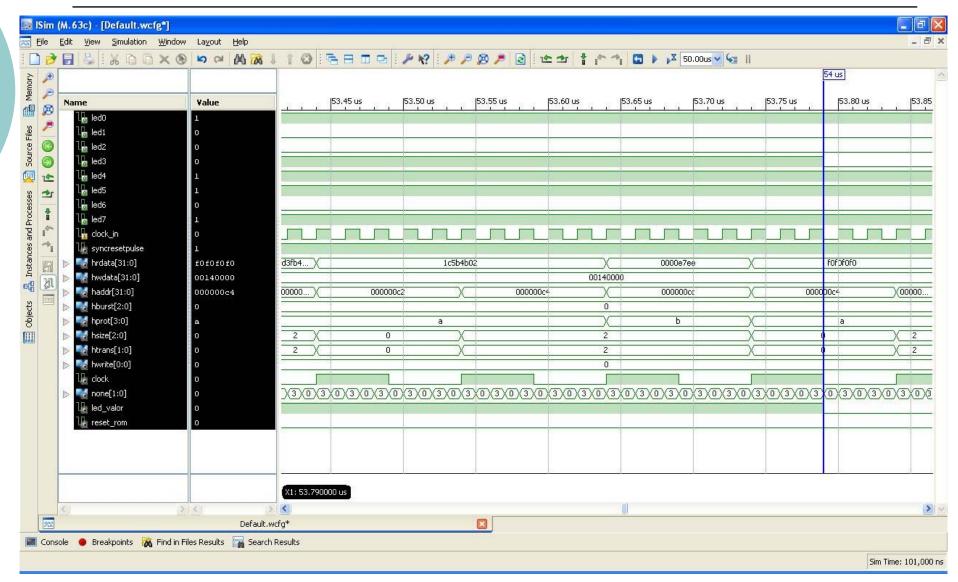

- Se utiliza la herramienta ISIM, simulador integrado del entorno Xilinx ISE.

- Se debe pasar de la vista de implementación a la vista de simulación:

Design→View: Simulation

- Es necesario forzar una entrada de reloj para la simulación, en este caso simularemos la salida del DCM:

- Seleccionamos la señal clock\_in y con el botón derecho del mouse seleccionamos "force clock"

- Luego simulamos 100 uS con esta configuración.

- Se observa que en el tiempo 53.79 uS se produce la aparición de la secuencia 0xf0f0f0f0 en el bus de datos de escritura (HWRITE), lo que produce la activación de la señal del detector del bus (Led03)

- Esto verifica el correcto funcionamiento del sistema en la simulación.

### Logros de esta etapa

Se ha verificado el correcto funcionamiento del sistema mediante una simulación funcional utilizando la herramienta ISIM del entorno Xilinx ISE

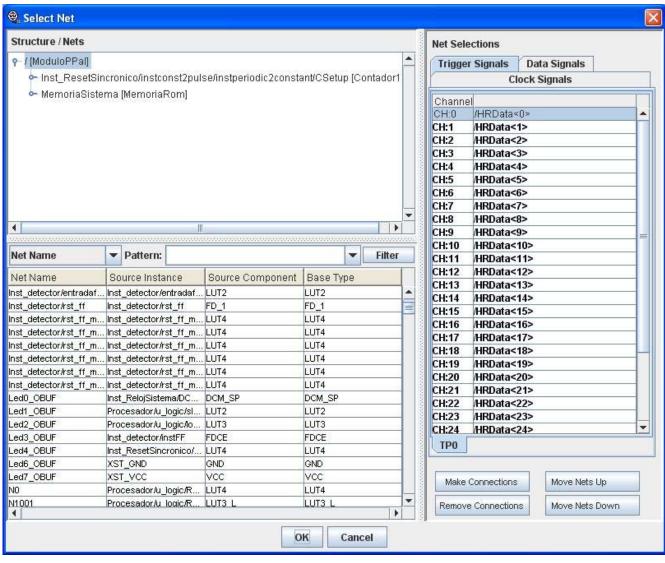

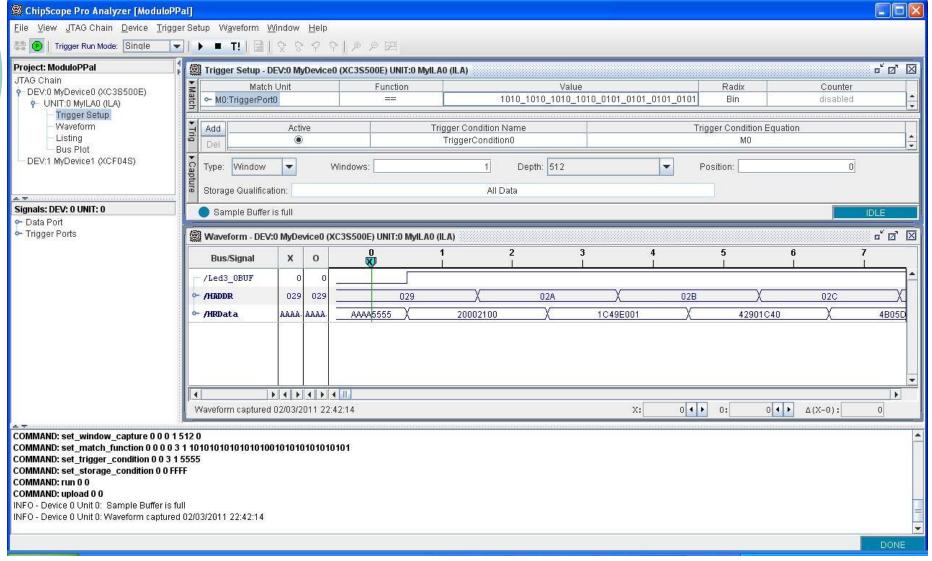

- Se utiliza la herramienta ChipScope Pro para visualizar las señales en el interior de la FPGA

- Se debe crear y configurar un módulo CSP:

- Se establece como condición de disparo la aparición del patrón 0xaaaa5555 en el bus HRDATA

- Se monitorean las señales HADDR, HRDATA y la salida del detector.

- Se utiliza como señal de reloj al reloj de sistema (HCLOCK)

Al darse las condiciones de disparo, se observa en el bus HRDATA la aparición del patrón Oxaaaa5555

### Logros de esta etapa

- Se verificó la aparición del patrón prestablecido en las señales internas de la FPGA

- Se obtuvo una concordancia entre la simulación de software en el entorno ARM MDK, la simulación funcional con ISIM y la verificación de hardware con ChipScope Pro.

### Información de contacto

Laboratorio de sistemas embebidos (LSE)

http://laboratorios.fi.uba.ar/lse

- Fabricio Baglivo baglivofabricio@gmail.com

- Pedro Martos

http://www.fi.uba.ar/~pmartos

pmartos@fi.uba.ar